古川弘介(ふるかわ・こうすけ)

海外勤務が長く、日本を外から眺めることが多かった。帰国後、日本の社会をより深く知りたいと思い読書会を続けている。最近常勤の仕事から離れ、オープン・カレッジに通い始めた。

◆はじめに

半導体産業復活に向けて、日本政府が巨額の支援をする複数のプロジェクトが進行中である。その中心に位置づけられるのは、北海道千歳市で2027年に最先端半導体の量産を目指すRapidus(ラピダス)(*注1)である。ラピダスは、民間企業8社(トヨタ、ソニー、NTTなど)が出資して設立されたが、実質的には政府肝煎りの国策会社である。補助金9200億円がすでに決まっているが、追加で4兆円程度の税金投入が必要だとみられる大プロジェクトなのである。

政府支援の大きさからもラピダスへの期待がうかがえ、まさに日本半導体産業復活の象徴となるプロジェクトといえる。しかし、ラピダスには課題が多い。

半導体技術者としてDRAM(メモリ半導体)“敗戦”を経験した湯之上隆(技術経営コンサルタント)は――日本はかつてメモリ半導体で世界一になったが、ロジック半導体では成功しなかった。したがってラピダスは「復活」ではなくて、ロジック半導体への「新たな」挑戦だ――と指摘する。その上で、それは「無謀な」挑戦だと批判するのである。

本稿では、湯之上の講義と著作を参考に、ラピダスを理解するためのキーワードを二つに絞り込んだ。第一は「微細化」である。半導体の歴史は微細化の歴史であり、勝負が決しつつある微細化競争の最前線に新規参入を図ることが、どれほどの困難さを伴うかについて理解する。

第二は「ファウンドリー」である。ラピダスが挑戦するのは、ロジック半導体のファウンドリー(受託製造会社)である。微細化が高度化するにつれてファウンドリーの設備投資額が膨れ上がっており、成功し続けるしか生き残る道は無くなっている事業だということを知る必要がある。

次に、二つのキーワードから導かれるラピダスの直面する課題について、技術、ビジネス、人材の面から検討した。参考資料は巻末に記した。

◆ラピダスを理解するための2つのキーワード

(1)微細化

⚫️テクノロジーノード

半導体集積回路は――スイッチ(0か1)として働くトランジスタという素子を集積して電子回路を構成したもの――である。集積度が上がると性能が向上するので、そのために微細化する。半導体の歴史を見ると、ムーアの法則(2年で2倍の集積化)(*注2)に沿う形で、集積化が進んできた。微細化の効果は、高集積化に加え、高速になる、低消費電力化する、コストが下がる、と良いことずくめである。しかし、微細化が進むほど技術的にクリアすべき課題が増えて、難易度が高まる。

半導体微細化の指標として「テクノロジーノード(技術の節目)」が使われ、ナノ(10億分の1)メートル(nm)で表示される。もともとはトランジスタのゲート長(信号を加える電極の長さ)を表す数字であったが、2次元から3次元へと微細化が進んで、現在は性能を表すメーカーの「商品名」に近いと考えるべきだという。ただ、そう言われてもイメージが湧かないので、半導体製造シェア世界トップのTSMC(台湾積体電路製造)のロジック半導体のテクノロジーノードの変遷を見ると下記のように進化していることがわかる(同社ホームページより抜粋)――

――⇨40nm(2008年) ⇨28/22nm(2011年) ⇨20nm(2014年) ⇨16/12nm(2015年) ⇨10nm(2016年) ⇨7nm(2018年) ⇨5nm(2020年) ⇨3nm(2022年)――

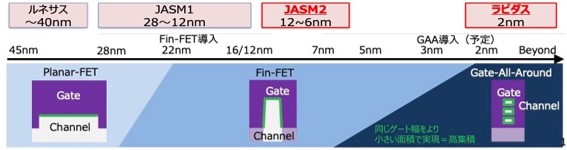

下図1は、テクノロジーノードの進化図の中での半導体メーカーの位置付けをイメージするためのものである。

図1:ロジック半導体のテクノロジーノード

(『半導体・デジタル産業戦略』(令和6年5月31日 経済産業省)から2つの説明図を取り出して作成)

(*注①:JASM1はTSMC熊本第一工場、同2は熊本第二工場)

(*注②:Planar-FETはトランジスタ形状が2次元構造、Fin-FETとGate-All-Around(GAA)は3次元構造)

日本トップの半導体メーカーであるルネサス(*注3)の実力は40nm止まりである。そこでTSMCを熊本に誘致して28nmから6nmまでのテクノロジーノードをカバーする。次に最先端半導体2nmの量産を国策会社のラピダスで行うというのが経済産業省の戦略である。

また、微細化が進むにつれトランジスタ形状も、上記「注」にあるように2次元から3次元に進化している。ラピダスの2nmのトランジスタ形状は最新のGAA構造であり、最新構造に切り替わるタイミングで新規参入を図ろうとしていることがわかる。

なお、28nm半導体は自動車向けの車載半導体に多く見られる。TSMCがそれを熊本で生産するのは、日本の自動車メーカー向けである。車載半導体の流れは――完成品メーカー(例えばトヨタ)が一次サプライヤーの部品メーカー(デンソー)に発注する⇨そこから二次サプライヤーの車載半導体メーカー(ルネサス)に発注する⇨ルネサスは40nmまでの半導体しか作れないので、それを三次サプライヤーのTSMCに製造委託する――である。

2021年初に、半導体不足により自動車が製造できないという異常事態が発生して、世界中で騒ぎになった。28nmのロジック半導体が不足したことが原因であるが、そのボトルネックになったのがTSMCであった。コロナ禍からの生産回復によってTSMCに発注が集中したため製造が逼迫(ひっぱく)したのである。世界中の車載半導体メーカーは28nmのロジック半導体をほぼ全てTSMCに製造委託しているので、TSMCが製造できなくなると世界中の自動車が造れなくなるのである。最先端半導体を必要とするAI(人工知能)についても同じことが言える。こうした事実が、地政学的リスクの高まりを背景に重みを増して、世界中で半導体製造拠点を自国に作りたい(=TSMCを誘致する)という動きにつながっていったのである。

また、TSMCは、テクノロジーノードに対応した工場を(需要がある限りどんなに古くても)維持していることが強みとなっている。減価償却(日本では5年)を終えた設備で古い世代の半導体も作っているということだ。これが高収益体質を作り、新規投資で失敗したとしてもカバーできる財務の強さにつながっていると思われる。ちなみに同社の営業利益率は47.5%(2024年第三四半期)と5割近い高水準を誇っている。

⚫️EUV(極端紫外線)露光装置

微細化のためには、半導体製造の前工程(後述)の中の露光が重要である。すなわち、より波長の短い露光装置を使えば、トランジスタ微細化につながる。その最先端露光装置が波長13.5nmのEUVである。

EUVは先端半導体(7nm世代以降)のロジック半導体製造に不可欠の装置であるが、オランダの半導体製造装置メーカーASMLホールディング(1984年設立)だけが供給できる。そのため、先端ロジック半導体メーカーではEUVの獲得競争が起きているといわれる。なお、残念ながら日本の露光装置メーカー(キヤノン、ニコン)には作れない。

TSMC、インテル、サムスンはEUVをすでに導入しているが、日本には一台もない。今回ラピダスが発注し、今年末ごろに導入される予定である。EUV露光は真空内で行われているので内部は真空部分が多くを占める重量200トンの巨大装置であり、価格は1台200億円以上といわれる。

また、非常に扱いにくいとされ、TSMCは早くからEUVを導入して、実際に露光して訓練を積んだ――2018年には100万枚のウェハーを露光して全てスクラップにしてEUVの訓練をした――という。その成果が現れて7nmの量産適応に成功し、5nmを経て現在3nmの量産を実現している。EUV保有台数は、TSMCが100台(2022年末)、サムスンが35台、インテルが15台である。湯之上は、日本ではEUVは今後5年でせいぜい5台程度の導入とみており、少ないがゆえにASMLの協力(ASMLは技術者養成のために台湾と韓国にはトレニングセンターを開設)が得にくく、EUV技術者の養成が課題となると指摘している。

TSMCが6年以上の時間とコストをかけて経験値を積み上げてきたEUVを、ラピダスはすぐに使いこなす必要があるのである。なお、後述する米IBMでのラピダス技術者の研修の重要テーマの一つは、そこに設置されているEUVの操作にある。

(2)ファウンドリー

半導体は、設計、前工程、後工程の3つの段階で作られる。ロジック半導体においては、ファブレスという設計専門の半導体メーカーが半導体を設計する。ファブレス(工場を持たないという意味)が設計したデータを基に、シリコンウェハー上に半導体を作るのが「前工程」である。シリコンウェハー(8〜12インチ)の上に約1000個の半導体が500〜1000の工程を経て作られる。この前工程を専門に行っているのがファウンドリーである。そして前工程で作られたチップを1個1個取り出して、パッケージに封入し、半導体の動作テストをするのが後工程である。アセンブリーメーカー、またはOSAT(*注4)と呼ばれる。

前稿で見たように、ロジック半導体は設計と製造のグローバルな水平分業が進んでいる。ファブレスは米国に約500社、台湾に200〜300社、中国に2800社以上あるが、企業別シェアランキングを見ると、クアルコム、ブロードコム、NVIDIA(エヌビディア)、AMDといった米国勢が上位に並んでいることからわかるように、先端半導体を必要とする有力企業は米国に集中している。ここに挙げた4社の製造はTSMCが行っている。なお、日本にはファブレスは5社程度しか存在しない。

一方、ファウンドリーは、TSMCがシェア60%超で首位であり、先端半導体に限れば90%以上のシェアを有して他を圧倒している。

これらの事実から分かることは――ラピダスは、顧客として先端半導体を必要とするファブレスを、米国、台湾などから見つけて製造を受託する必要がある。競合するのは先端半導体で圧倒的シェアを握るTSMC――である。

このようにラピダスは技術面、ビジネス面が大きな課題となっている。さらにそれらに加えて人材面でも不安材料がある。次に3つの面から課題について考えたい。

◆課題1:技術面:量産化技術の難しさ

⚫️微細化の土台がない

半導体は毎世代微細化を追求していくが、解決すべき課題は上に行くほど多く、難しくなる。前述のように日本の土台は40nmまでである。ここから2nmにたどり着くまでの間には(TSMCのテクノロジーノードに従えば)7世代(14年間)の微細化世代があるが、日本にはその技術的蓄積がない。したがってラピダスにはアップデートすべき「土台」がない。

湯之上は「土台」の重要性について、インテル(垂直統合型)の例――最先端競争をしていたが、14nmで5年以上立ち上げができなかったことが尾を引いて、競争から脱落――を挙げる。インテルの教訓として「一度狂った微細化の『時計の針』は二度と元に戻らない」ことを指摘する。土台があってもいったん後れを取ると、追いつけないほど引き離されるのに、土台そのものがない状態で、先頭を走るTSMCレベルに追いつくことは至難というのである。

⚫️IBMの支援と量産化技術

こうした状況は、ラピダスやそれを支援する政府は当然承知しているはずである。にもかかわらず最先端半導体に挑戦する理由については、安全保障上の理由以外に、技術面ではIBMの存在が大きいと思われる。すなわち――IBMから日本企業に先端半導体の製造について打診があり、IBMが技術の供与を行うこと――が決め手になったのではないか。また、ベルギーの半導体研究機関で、新EUVをASMLと共同で開発中のimec(*注5)もラピダスの支援で合意している。ラピダスは自前主義を捨てて、世界の半導体エコシステムの一員として出発を図ろうとしている点は評価すべきだろう。

ラピダスの技術者が研修を受けているのは、IBMの先端半導体開発拠点であるオールバニ・ナノテク・コンプレックス(米ニューヨーク州)で、ここでIBMが世界で初めて2nm半導体の開発に成功している。ラピダスは2023年4月の第一陣以降、技術者のべ200人を派遣する見通しで、すでに前述のEUV露光装置の扱い方などを学んでいるという(*注6)。

しかし、湯之上は、IBMの2nmの技術は研究所段階のものであり、量産できるか、コストを抑えられるかという量産技術とは違うと指摘する。量産技術には経験値が重要な働きをするということである。新規参入で技術的土台のないラピダスが、最先端半導体の量産を実現できるかは、現状未知数と言わざるを得ない。

◆課題2:事業サイクルを回せるのか

⚫️ファウンドリー事業の難しさ

すでにみたように、最先端半導体を求めるファブレスの獲得は大きな課題ではあるが、ラピダスは、TSMCのようにアップルやNVIDIAのようなトップクラスの大口顧客を対象としているわけではないと思われるので、中小ファブレスがターゲットになるのだろう。半導体“敗戦”の原因の一つであった「マーケティング軽視」は教訓として生かされていると思われ、すでに米国カリフォルニア州にファブレス向けの営業拠点を設けている。今後の営業努力である程度の受注は可能かもしれない。

しかし問題は、顧客の獲得だけではなく、設備能力を満たすに十分な顧客を獲得して稼働率を高めることでキャッシュフローを稼げるかという点にある。それを次期製品の開発・設備投資に回せなければ、先端半導体競争に参加し続けることはできず、生き残れないというのがファウンドリー事業の難しさであり、厳しさだからである。

こうしたファウンドリー事業の困難さを認識させたのが、米国を代表する半導体メーカーのインテルの不振である。同社は、設計と製造を自社で行う垂直統合型モデルで、TSMCと先端半導体で競争をしていたが、微細化に後れを取ったことで業績が悪化した。経営陣が交代し、2021年にファウンドリー事業への参入を表明した。しかし、その先行投資が嵩(かさ)んで赤字が膨らみ、今年8月には人員削減と配当停止を表明する事態に至った(*注7)。不振の原因の一つに「大口顧客の不在」が挙げられており、TSMC一人勝ちの中での先端半導体向け大口顧客獲得の難しさがわかる出来事である。

インテルが陥った事態が示唆するのは――ファウンドリー事業は微細化の進行とともに巨額の投資が必要なリスクの高いビジネスになっている(TSMCの毎年の設備投資額は約300億ドル〈4.5兆円〉である)――ということである。ラピダスが挑戦するファウンドリー事業は、こうした特性を持つことを認識しておく必要があると思われる。

⚫️ TSMCによる受託生産のプラットフォーム構築

今回、湯之上の講義を聞いて、自分の常識を覆される経験をした。それはファブレスとファウンドリーの関係である。設計を行うファブレスが、ファウンドリーに製造を委託するのだから、ファブレスの方が優位な立場にあると考えていた。しかし、かつてはそうであったとしても、現在はむしろ立場が逆転しているというのである。

ファブレスにとって最大の問題は、新しく設計して前工程で作った半導体チップが動作しない場合である。そうなれば新興ファブレスは倒産するリスクがある。そこでTSMCは、設計、前工程、後工程を徹底的に水平分業し、それぞれの世界標準化を推し進めることによってこうした問題を解決したのである。すなわち――設計は、回路設計データ(セル)を提供するベンダー、設計ツール(EDA)ベンダー、ファブレスによる分業が行われている。TSMCは、世界標準の設計ツール(EDA)ベンダーと協力して、設計ツールに、セルと呼ばれる数百種類の機能モジュールを搭載した――のである。

これによってTSMCに生産委託するファブレスは、EDAツールに搭載されたセル・ライブラリーから、必要なセルを選択して設計すれば済む。こうして回路設計データ提供ベンダー、EDAツールベンダー、ファブレス、前工程メーカー(TSMC)、後工程メーカーによるエコシステム(生態系)が形成されたのである。

世界標準のEDAツールには、動作が検証されたセルが多数搭載されている。したがってファブレスは必要なセルを選択して設計すれば、動作の心配はない。ファブレスは、TSMCに生産委託することで、ほとんどリスクなく半導体を生産してもらえるようになったのである。湯之上が言うように、TSMCは、受託生産のプラットフォームを構築することに成功したのであり、TSMCの半導体工場は「世界のインフラ」となったのである。だから世界のファブレスは、TSMCに駆け込むのである。

ここから言えることは――TSMCは、単なるファウンドリーではなくプラットフォーマーと呼ぶべき存在である。したがってラピダスは、たとえ先端半導体を作れたとしてもTSMCと競争できない――である。

◆課題3:人材:半導体人材確保が困難

すでに見たように、半導体の製造工程は、設計(ファブレス)、前工程(ファウンドリー)、後工程(OSAT)に分かれる。ファウンドリーが担う前工程は、洗浄⇨成膜⇨リソグラフィー(基板に光や電子ビームなどで回路パターンを転写する手法)⇨エッチング⇨洗浄⇨検査、に分かれる。

湯之上は前工程に必要な技術者について下記のように試算する――

①それぞれの要素技術に関し、数百人以上の技術者が必要(精鋭集団)

②要素技術を組み合わせて工程フローを構築する技術(インテグレーション技術)についても100人程度の技術者が必要(タレント集団)

③生産技術として開発センターから量産工場への技術移管に関して、技術者1000人程度必要である(熟練技術者)

④量産工場では品質と歩留まりが重要であるので、2nmの生産には合計で1500人以上の技術者が必要である

湯之上は「ラピダスにはこれらの技術者を集めることができるとは思えない」と述べている。その根拠として日本の半導体技術者数の減少を挙げる。すなわち――ピーク時の1995年には20.62万人いたが、2019年には6割減の8.27万人に減少――である。ラピダスの現在の社員数は300人程度(TSMCは社員総数8万人、毎年6000人を採用)であるが、必要人員1500人の技術者確保については楽観できないと思われる。

技術者の「数(量)」の確保が課題であるだけではなく、「質」についても懸念があることについて述べたい。「TSMCのすごさ」を表すエピソードは多いが、中でも「研究開発部門は24時間稼働(日勤、準夜勤、夜勤の3シフト)」は、同社の企業体質を象徴している。これは2014年に10nm半導体の量産技術の開発を切れ目なく行うために、当時の張忠謀(モリス・チャン)董事長(創業者)の決断で実施した体制である(2016年に10nm量産成功)。研究開発部門の24時間稼働は珍しいというが、ファウンドリーにはそれだけのスピード感が必要だというモリス・チャンの危機感を、全社で共有することに役立ったのではないかと考える。

このようにTSMCは、ファウンドリーとしての危機感を全社で共有することに成功しているが、その企業文化は、技術者的合理主義に立脚したモーレツ主義とされる。そうしたTSMCが熊本で、「日本人は働かない」と不満を持っているという記事を目にした(*注8)。働き方改革を推進する日本に、TSMC的モーレツ主義は合わないかもしれない。しかし、ラピダスはそのTSMCと競争していかなければならないことだけは、忘れてはならないと思う。

◆まとめ

⚫️ラピダスの課題は多い

ラピダスの課題を技術面、ビジネス面、人材面から検討した結果は――

①技術的難易度が非常に高く、技術的土台のない新参のラピダスが克服できるかは現状未知数

②半導体量産を成功させて、そのキャッシュフローを次期製品の研究開発・設備の投資に回すファウンドリーの事業サイクルを回せない可能性が高い

③必要な半導体技術者を確保できない可能性がある

⚫️3つのシナリオ

このような厳しい状況の中では、ベストシナリオだけではなくワーストシナリオ、ニュートラルシナリオについて、準備しておくのは当然だと思われる。そこで3つのシナリオを考えてみた。

ベストシナリオは①②③全てがうまくいくケース、ワーストシナリオは全て実現しないケースである。この中間にニュートラルシナリオの設定をした。①③は(遅延があったとしても)なんとか達成するケースである。より現実的なケースだと思われる。

問題は、この場合でも②の実現は必ずしも保証されないということにある。設備の稼働率が上がらず、十分なキャッシュフローが稼げなければ、次期先端半導体(1.5nm)量産への巨額投資が賄えない。ファウンドリーにとって、事業サイクルが回せなければ微細化競争から脱落することを意味する。それを避けようとすれば、政府による追加の資金支援が必要だ。(その時点で5兆円投入しているかもしれない)ラピダスに、さらに税金を投入することになる。

政府は、追加の出資や融資の形での民間企業の関与を深めようと動いているようであるが、リスクの大きさを考えれば簡単には乗ってこないと思われる。将来、政治が判断を求められることになるのではないか。現在の石破内閣にその覚悟はあるのだろうか。さらに一連の半導体産業復活プロジェクトを推進してきた自民党の甘利明半導体戦略推進議員連盟会長が、今年10月の衆議院選挙で落選したため、推進力低下が懸念されていることも不安材料である。

いずれにせよ、最も避けるべきは、政治的判断を下すことを嫌い、かといって破綻(はたん)させる勇気もなく、ただ延命のためだけに、追加で資金(税金)を投入し続けることであるのはいうまでもない。

<参考書籍など>

『半導体有事』(湯之上隆著、文春文庫、2023年4月20日初版)

<受講講座>

「間違いだらけの日本半導体政策――今も昔も『経産省が出てきた時点でアウト』」(湯之上隆講師、早稲田大学オープンカレッジ〈2024年4月13日、5月11日、6月1日、6月15日の4回、各1時間半〉)

(*湯之上隆:1987年日立に入社して半導体開発に携わる。日立退職後、同志社大学客員教授を経て現在は技術経営コンサルタント、微細加工研究所所長。工学博士)

(*注1)Rapidus株式会社:本社は東京都千代田区(工場は北海道千歳市)、設立日:2022年8月10日、資本金73億4600万円、会長:東哲郎(元東京エレクトロン社長・会長)、社長:小池淳義(工学博士、日立半導体グループ生産技術本部長、トレセンティテクノロジーズ社長、ウエスタンデジタルジャパン社長)(出所:同社ホームページ)

(*注2)ムーアの法則:インテル創業者の一人であるゴードン・ムーアが唱えた経験則に基づく将来予測(出所:Wikipedia)

(*注3)ルネサスエレクトロニクス株式会社:資本金1532億円、従業員21200人。日立製作所と三菱電機の半導体事業(ロジック、アナログ、〈DRAM除く〉メモリ他)を分社化して2003年4月にルネサステクノロジ株式会社を設立。2010年4月にはNECから分社化していたNECエレクトロニクスと経営統合してルネサスエレクトロニクス株式会社が設立され現在に至る(出所:Wikipedia)

(*注4)OSAT:Outsourced Semiconductor Assembly and Test

(*注5)imec(Interuniversity Microelectronics Centre)ベルギーに本部を置く国際研究機関。1982年創設。次世代エレクトロニクス技術の開発に取り組んでいる。2022年12月6日にラピダスと長期的な協業に向けて合意した(出所:Wikipedia)

(*注6)「IBM、2ナノ半導体『模擬』工場 ニューヨーク研究所で量産開発 ラピダス技術者100人結集」(日本経済新聞、2024年5月29日付)

(*注7)「インテル垂直統合モデルに岐路 製造分社化で外部資金調達」(日本経済新聞、2024年9月29日付)

(*注8)「TSMC、全国行脚『昼夜問わず仕事できる人材』」(日経ビジネス、2024年10月11日)

コメントを残す